SMIC urges China’s chipmakers to embrace advanced packaging as Moore’s Law slows nanometre node progress and US sanctions bite

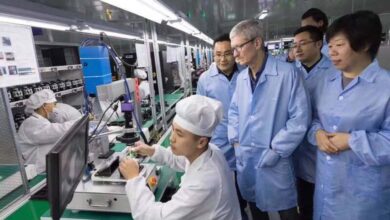

Chinese chip makers should focus on developing advanced packaging technologies to overcome their weakness in nanometre process nodes, according to Chiang Shang-yi, the former TSMC R&D director recently recruited by Semiconductor Manufacturing International Corp (SMIC).

Chiang, SMIC’s executive director and vice-chairman, said future breakthroughs for the country’s integrated circuit (IC) manufacturing industry would come from advanced packaging techniques that can cram more circuits into smaller packages, a necessary requirement as Moore’s Law inches towards its physical limits.

The remarks, Chiang’s first in public since joining the company in December, could signal a shift in focus at the Shanghai-based wafer foundry which has seen its prospects for closing the technology gap with much bigger rival Taiwan Semiconductor Manufacturing Co (TSMC) dimmed by US sanctions.

Chiang’s comments were made at the closed door China IC Conference earlier this month and first reported over the weekend by Moore News, a Chinese semiconductor industry website that was the official media partner of the event.

SMIC did not immediately reply to a request for comment.

The appointment of Chiang triggered a boardroom clash at SMIC, with co-CEO Liang Mong Song, his former lieutenant at TSMC, threatening to quit after complaining he was not informed of the decision in advance. However, Liang is still with the company, according to stock filing posted on SMIC’s website.

Chiang told the IC conference that he has been fascinated by the development of advanced packaging over the past decade and believes that the technology will be crucial in the post Moore’s Law era. In 1965 Gordon Moore, who would later co-found US chip maker Intel, predicted the number of transistors on an IC would double roughly every two years. Moore’s Law has held since despite many experts predicting it would hit a brick wall

Analysts said SMIC will need to combine IC packaging and wafer foundry expertise to remain competitive in the industry, especially after the US sanctions blocked its access to leading edge semiconductor manufacturing equipment from US and European suppliers.

“SMIC is likely to develop both advanced [wafer processing] nodes and chip packaging,” said Eric Tseng, chief executive of Taiwan-based semiconductor analysis firm Isaiah Research.

SMIC’s strategy under US sanctions may be to focus on mature processes but use advanced packaging technologies to boost the performance of its chips, Tseng said.

Gu Wenjun, chief analyst at Shanghai semiconductor research firm ICwise, agrees that it would be pragmatic for SMIC to focus on older nodes amid the US restrictions because there is still robust demand for mature foundry services from China’s domestic semiconductor design companies.

Chiang told the 400 industry delegates at the IC conference that the global semiconductor industry was facing bottlenecks in continuing to push ahead with advanced nanometre nodes given the huge investments required, coupled with the reduction in number of clients that require the most advanced chips.

Only a handful of high-volume IC products would need to be made using advanced nodes, he said.

A new wafer fab capable of 5nm production is expected to cost US$15 billion, twice as much as the earlier generation 14nm fabs operated by SMIC, according to data from International Business Strategies, cited by SMIC in its recent prospectus.

Other speakers at the IC conference echoed Chiang’s view. “The single-minded development of advanced process nodes will be more difficult,” said Wu Hanming, dean of the School of Micro-Nano Electronics at Zhejiang University, adding that there was plenty of market potential for mature nodes.

The so-called back end operation, also known as outsourced semiconductor assembly and test (OSAT), is the final stage in the highly complex chipmaking process and has traditionally been handled by specialist factories in Asia.

This is not the first time SMIC has taken an interest in the packaging side of the industry. In 2014, it established a joint venture SJ Semiconductor Corp with China’s JCET Group, the third largest OSAT company after ASE of Taiwan and Amkor of South Korea. JECT’s sales accounted for 11.3 per cent of the global semiconductor packaging and testing market, versus 30.5 per cent for ASE and 14.6 per cent for Amkor, according to JCET’s 2019 annual report.

Advanced semiconductor packaging is moving from substrate platforms to silicon wafers in a paradigm shift that is providing opportunities for foundry leaders like TSMC and Samsung Electronics, according to analysts.

This article appeared in the South China Morning Post print edition as: Sector told to cram more circuits into smaller packages

Source link